Block diagram of dma controller

Home » Background » Block diagram of dma controllerYour Block diagram of dma controller images are available in this site. Block diagram of dma controller are a topic that is being searched for and liked by netizens today. You can Get the Block diagram of dma controller files here. Download all free vectors.

If you’re looking for block diagram of dma controller pictures information connected with to the block diagram of dma controller interest, you have pay a visit to the right site. Our website always provides you with suggestions for seeing the maximum quality video and picture content, please kindly hunt and locate more informative video content and images that fit your interests.

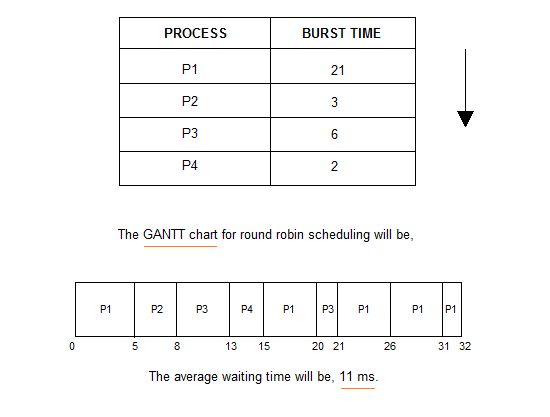

Block Diagram Of Dma Controller. Typical DMA Block Diagram After the information are sent the processor continues with other work. It is the low memory read signal which is used to read the data from the addressed memory locations during DMA read cycles. Block DMA transfer supports faster IO data transfer rates but the CPU remains inactive for relatively long period. Dma controller is a hardware device that allows i o devices to directly access memory with less participation of the processor.

New Digital Signal Controller Dsc Accelerates Dsp Performance For Time Critical Control Applications Pic Microcontroller Electronic News Digital Signal Processing From in.pinterest.com

New Digital Signal Controller Dsc Accelerates Dsp Performance For Time Critical Control Applications Pic Microcontroller Electronic News Digital Signal Processing From in.pinterest.com

This read-only register reflects the overall operating status of all channels in the DMA Controller. In this class we will understand Block Diagram of DMA Controller. Isolated IO or IO Mapped IO Memory Mapped IO Asynchronous Data Transfer Using Strobe Control Mechanism. Types of DMA transfer1DMA transfer block In this DMA mode DMA controller is master of memory bus. The LPC1768666564 are ARM Cortex-M3 based microcontrollers for embedded applications. The Intel is a 4-channel direct memory access DMA controller.

DMA Status Register DSTR.

ArchitectureFunctional block diagram of 8257 DMA controller. Direct memory access dma. 8257 dma controller block diagram pdf Posted on August 28 2021 PROGRAMMABLE DMA CONTROLLER INTEL It is a 40 pin IC and the pin diagram is The functional block diagram of is shown in fig. Mode set register and a terminal count register and it can also program control registers of DMA controller through the data bus. The 8237 is actually a special-purpose micro- processor whose job is high-speed data transfer between memory and the IO. Block Diagram of DMA Controller.

Source: pinterest.com

Source: pinterest.com

Fig-1 below shows the diagram of the DMA controller. 8257 DMA stands for 4-channel Direct Memory Access. Fig-1 below shows the block diagram of the DMA controller. The DMA transfer needs only 5 clock cycles. Normal transfer of one data byte consumes to 29 clock cycles.

Source: pinterest.com

Source: pinterest.com

Give block diagram of DMA controller. Mode set register and a terminal count register and it can also program control registers of DMA controller through the data bus. The 8237 is actually a special-purpose micro- processor whose job is high-speed data transfer between memory and the IO. Dma controller needs the same old circuits of an interface to communicate with the cpu and input output devices. Typical DMA Block Diagram After the information are sent the processor continues with other work.

Source: pinterest.com

Source: pinterest.com

Dma controller needs the same old circuits of an interface to communicate with the cpu and input output devices. The 8237 DMA controller supplies the memory and IO with control signals and memory address information during the DMA transfer. Typical DMA Block Diagram After the information are sent the processor continues with other work. Block Diagram Showing DMA. 8237 DMA Controller Block Diagram Control Logic.

Source: pinterest.com

Source: pinterest.com

8257 dma controller block diagram pdf Posted on August 28 2021 PROGRAMMABLE DMA CONTROLLER INTEL It is a 40 pin IC and the pin diagram is The functional block diagram of is shown in fig. The 8237 DMA controller supplies the memory and IO with control signals and memory address information during the DMA transfer. Then the microprocessor tri-states all the data bus address bus and control bus. Er Abhishek Kumar Agrahari Microprocessor 439 Views. This read-only register reflects the overall operating status of all channels in the DMA Controller.

Source: in.pinterest.com

Source: in.pinterest.com

Introduction Direct memory access DMA is a process in which an external device takes over the control of system bus from the CPU. Block Diagram of In general it loses any overall speed benefit associated with DMA but it may be necessary if a peripheral requires to be accessed by DMA due to either demanding timing requirements or hardware interface inflexibility. The DMA module then transfers the entire block of data directly to. The block diagram shows a logical pin out and internal registers of the 8237. Block Diagram of DMA Controller.

Source: pinterest.com

Source: pinterest.com

The LPC1768666564 are ARM Cortex-M3 based microcontrollers for embedded applications. DACK o DACK 3. Normal transfer of one data byte consumes to 29 clock cycles. Draw and explain the block diagram of DMA controller. The figure below shows the pin diagram of 8257 DMA controller.

Source: tr.pinterest.com

Source: tr.pinterest.com

Types of DMA transfer1DMA transfer block In this DMA mode DMA controller is master of memory bus. Then the microprocessor tri-states all the data bus address bus and control bus. The Intel is a 4-channel direct memory access DMA controller. ArchitectureFunctional block diagram of 8257 DMA controller. Mode set register and a terminal count register and it can also program control registers of DMA controller through the data bus.

Source: pinterest.com

Source: pinterest.com

Block Diagram of 8237. Introduction Direct memory access DMA is a process in which an external device takes over the control of system bus from the CPU. Direct memory access dma. It is specifically designed. DMA Status Register DSTR.

Source: in.pinterest.com

Source: in.pinterest.com

Two 16-bit registers are internally associated with each channel These registers. It is specifically designed. Block Diagram of 8237. DMA Status Register DSTR. Then the microprocessor tri-states all the data bus address bus and control bus.

Source: pinterest.com

Source: pinterest.com

Mode set register and a terminal count register and it can also program control registers of DMA controller through the data bus. The ARM Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The 8237 DMA controller supplies the memory and IO with control signals and memory address information during the DMA transfer. Types of DMA transfer1DMA transfer block In this DMA mode DMA controller is master of memory bus. This read-only register reflects the overall operating status of all channels in the DMA Controller.

Source: pinterest.com

Source: pinterest.com

DMA Status Register DSTR. DMA controller provides an interface between the bus and the input-output devices. 8257 DMA stands for 4-channel Direct Memory Access. The Intel is a 4-channel direct memory access DMA controller. The LPC1768666564 operate at CPU frequencies of up to 100 Mhz.

Source: pinterest.com

Source: pinterest.com

Fig 1 below shows the block diagram of the dma controller. Pin Diagram of Outputs. Fig-1 below shows the block diagram of the DMA controller. In this class we will understand Block Diagram of DMA Controller. Er Abhishek Kumar Agrahari Microprocessor 439 Views.

Source: pinterest.com

Source: pinterest.com

Block Diagram of In general it loses any overall speed benefit associated with DMA but it may be necessary if a peripheral requires to be accessed by DMA due to either demanding timing requirements or hardware interface inflexibility. In this class we will understand Block Diagram of DMA Controller. Block DMA transfer supports faster IO data transfer rates but the CPU remains inactive for relatively long period. Introduction Direct memory access DMA is a process in which an external device takes over the control of system bus from the CPU. It is the low memory read signal which is used to read the data from the addressed memory locations during DMA read cycles.

Source: cz.pinterest.com

Source: cz.pinterest.com

Block DMA transfer supports faster IO data transfer rates but the CPU remains inactive for relatively long period. Dma controller is a hardware device that allows i o devices to directly access memory with less participation of the processor. Typical DMA Block Diagram After the information are sent the processor continues with other work. The block diagram shows a logical pin out and internal registers of the 8237. Mode set register and a terminal count register and it can also program control registers of DMA controller through the data bus.

Source: pinterest.com

Source: pinterest.com

Through the use of the address bus and allowing the DMA and RS register to select inputs the register within the DMA is. Dma controller needs the same old circuits of an interface to communicate with the cpu and input output devices. The unit communicates with the CPU through knowledge bus and control lines. In summary the DSP56300 DMA can perform IO and memory accesses that are independent of and frequently simultaneous with PCU operations. Er Abhishek Kumar Agrahari Microprocessor 439 Views.

Source: id.pinterest.com

Source: id.pinterest.com

Dma controller is a hardware device that allows i o devices to directly access memory with less participation of the processor. Block DMA transfer supports faster IO data transfer rates but the CPU remains inactive for relatively long period. DRQ 0 to DRQ 3 Pin number 16 to 19 These pins get enabled whenever the input device requests the DMA controller for direct data transfer to or from the main memory. The Intel is a 4-channel direct memory access DMA controller. DACK o DACK 3.

Source: pinterest.com

Source: pinterest.com

Types of DMA transfer1DMA transfer block In this DMA mode DMA controller is master of memory bus. It also shows the interface with the 8085 using a 3-to-8 decoder 8237 has four independent channels CH0-CH3. In this class we will understand Block Diagram of DMA Controller. Draw and explain the block diagram of DMA controller. This mode is needed by the secondary memory like disk drives that have data transmission and are no to be stopped or slowed without any loss of data transfer of blocks.

Source: pinterest.com

Source: pinterest.com

DMA can transfer memory-to-memory and handle mixed multi-dimensional and special address mode transfers. ArchitectureFunctional block diagram of 8257 DMA controller. Through the utilization of the address bus and permitting the DMA and RS register to pick out inputs the register among the DMA is chosen by the CPU. Typical DMA Block Diagram After the information are sent the processor continues with other work. Block DMA transfer supports faster IO data transfer rates but the CPU remains inactive for relatively long period.

This site is an open community for users to do submittion their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site convienient, please support us by sharing this posts to your preference social media accounts like Facebook, Instagram and so on or you can also bookmark this blog page with the title block diagram of dma controller by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.